A little bit about myself…

Hi! I’m Dias, a graduate student at the Department of Electrical and Computer Engineering in UBC. Right now I’m conducting research on the topic of cosimulation of electronic circuits along with Silicon Photonics devices for various applications (e.g. optical data transmission links). Generally, my research interests include CMOS electronics, Silicon Photonics, and applied Machine Learning. This website is intended to serve as a place where you can see all my projects and past experience. Soon I am planning to write blogs on the topics that interest me. Feel free to get in touch with me via email or using the form at the end of this page.

- CMOS analog and digital electronics

- Silicon Photonics

- Machine Learning

-

MASc in Electrical and Computer Engineering, November 2023 (expected date)

University of British Columbia

-

BEng in Electrical and Electronic Engineering, 2020

Nazarbayev University

Experience

- Working on Verilog-A modelling of Silicon Photonic (SiP) devices for optical transceivers and neuromorphic applications.

- Taped out the 1.2V Bandgap Voltage Reference circuit in TSMC65. The maximum PVT variation was reduced down to 28 mV across all PVT corners. Also developed and post-layout verified the 1V and 2.5V versions of the circuit for the next run.

- Enabled electro-optic cosimulation of coherent link in Cadence Virtuoso by creating a Verilog-A SiP library. Using the library designed and simulated 100 Gbps DP-QPSK coherent link that includes active and passive Silicon Photonics elements and transistor-level drivers and TIAs (45 nm CMOS).

- Helped in integration and debugging of Synopsys Optocompiler for electro-optic cosimulation.

- Delivered workshops on Linux and Git to undergraduate students. Also ran lab sessions and tutorials involving DE1-SoC FPGA board programming for “Introduction to Microcomputers” course.

- Wrote a program in Python that extracts various statistical data about phone call recordings (SNR, speech length etc.) and preprocesses them along with open-source datasets for Automatic Speech Recognition. Used this preprocessed dataset, which is comprised of bilingual speech, to train hybrid HMM-DNN models in Kaldi and achieved 43% WER within 3 months of model development.

- Built robust scalable address converter in Java via Apache Lucene and Regex. The final accuracy is 91% (i.e. the program can match 91 out of every 100 raw addresses), the time it takes to find matches from database to 10000 inputs is 1 hour. The matched addresses (text data) are then used to obtain their approximate geocoordinates via ArcGIS engine.

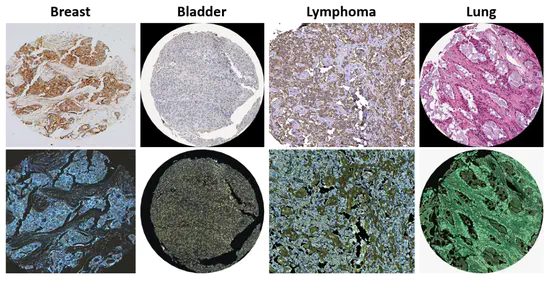

- Developed a Machine Learning based web application which can in live mode detect different cancers and determine the type of cancers with an accuracy of over 99% based on the images uploaded by a user. Frontend is implemented in Python Flask, Backend is built via Keras and consists of 9 CNNs.

- Using Python created a website that visualizes the risk of getting COVID-19 in major cities of Kazakhstan. The data is automatically updated each day.

- Built a pipeline in Python for preprocessing and classifying human brain signals with Transfer Learning as part of Brain-Computer Interface project (72% accuracy, subject-independent testing).

- Designed seven basic SiP logic gates in Ansys Lumerical through microring resonators and heaters. Results are published in several SPIE conferences and in an academic journal.

- Developed a script in Python for extracting statistical data from 5 torrent tracker websites through HTML parsing. The findings were presented at the CoCoNet 2018 conference.

- Designed several NEM relay-based power converters (DC-DC, AC-DC, and DC-AC) using switched-capacitor topology. Results are published in the ISCAS 2020 conference proceeding.

Projects

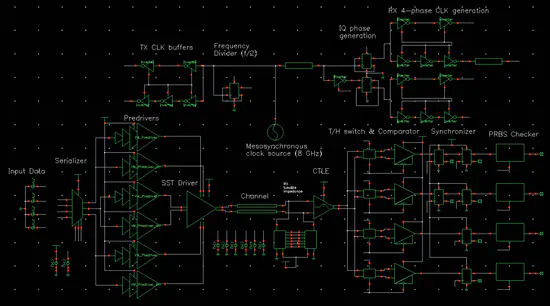

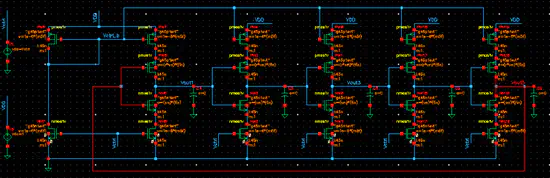

16 Gbps high-speed I/O link

16 Gbps high-speed I/O link over a lossy backplane channel in Cadence Virtuoso (65 nm CMOS)

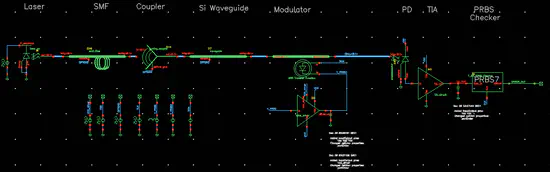

30 Gbps Silicon Photonics link

30 Gbps SiP data transmission link in Cadence Virtuoso (65 nm CMOS)

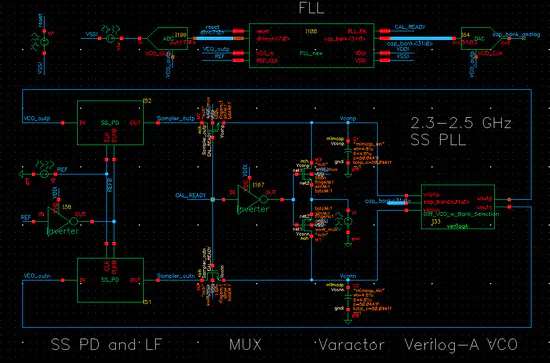

Sub-Sampling LC-PLL design

Design, Analysis and Simulation of a Frequency Synthesizer using Analog Sub-Sampling LC-PLL (65 nm CMOS)

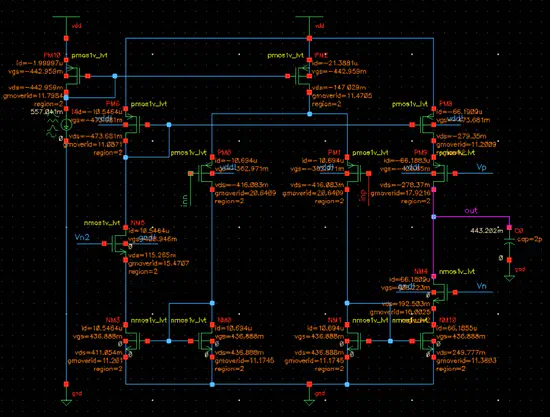

Two-Stage OTA design using gm/Id methodology

Two-Stage OTA design and analysis using gm/Id methodology (45 nm CMOS).

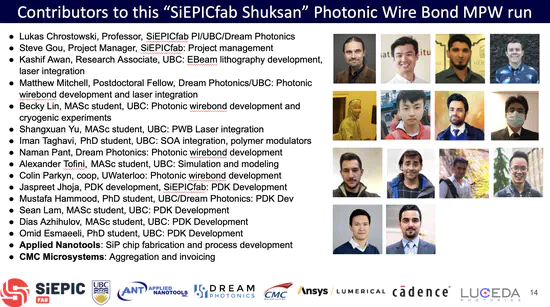

SiEPICfab Shuksan PDK

Developed from scratch a new PDK using in-house developed layermap and technology files

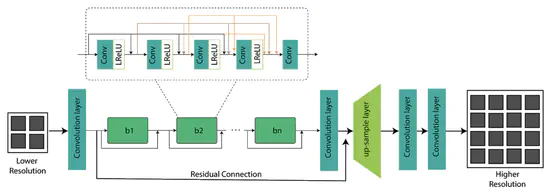

Single image super-resolution

Built an HDR image upscaling GAN (8x upscaling) in PyTorch using ESRGAN architecture as a reference

Voltage Controlled Oscillator (VCO)

Comparison of different VCO designs for PLLs

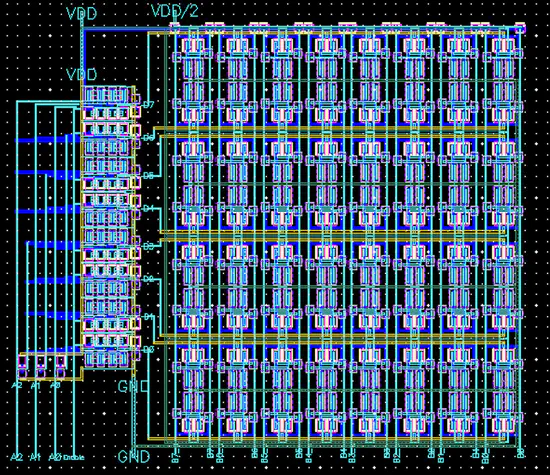

6T SRAM memory cell design and layout

6T SRAM memory cell design and layout in 65nm node

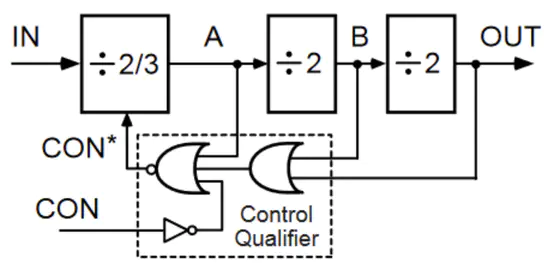

Variable frequency divider

Variable frequency divider for PLLs with a logic circuit to switch between different frequency bands

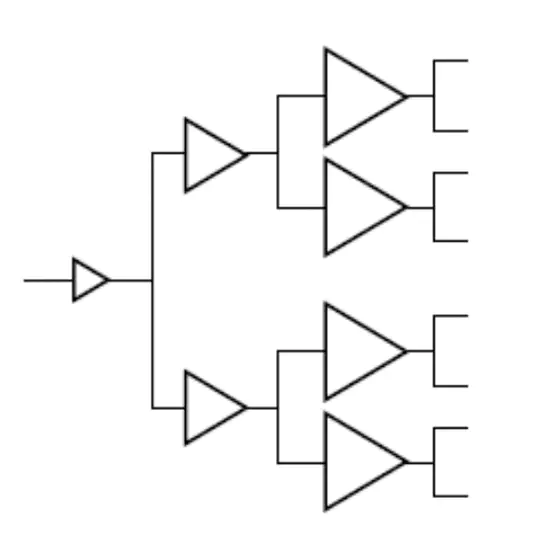

Clock distribution network

Designed clock distribution network using numerous buffer stages to minimize the delay, rise and fall times, skew, and power consumption of the network

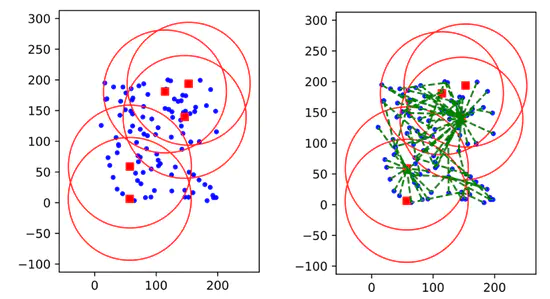

Wireless Sensor Network optimization

Python algorithm for equal distribution of sensors among base stations

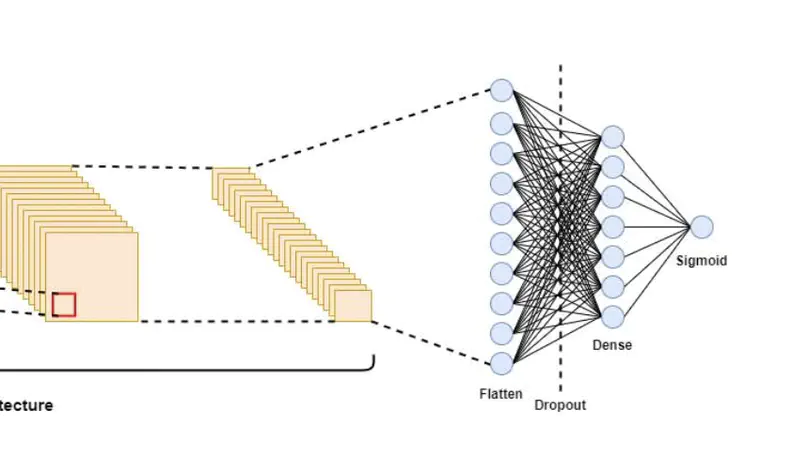

Histopathological classification of cancer via Deep Learning

Automating cancer detection & classification using pre-trained CNNs

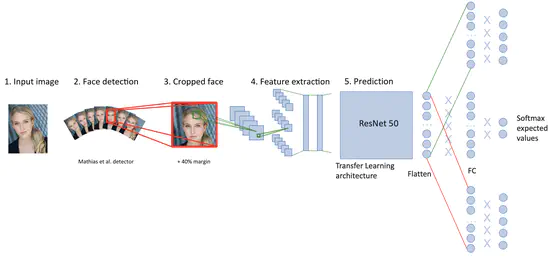

Apparent Age, Gender and Ethnicity Prediction

Apparent Age, Gender and Ethnicity Prediction using Deep Learning techniques

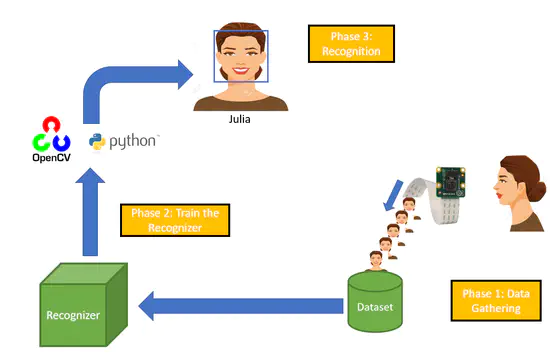

Facetendance

Real-time face recognition system on Raspberry Pi 3 for automated attendance monitoring

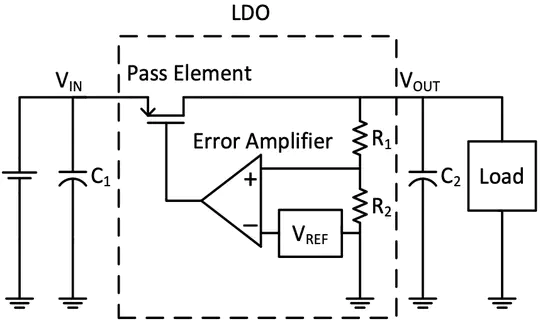

Error Amplifier in LDO

Analysis of the role of Error Amplifier in the context of Low-Dropout Voltage Regulators.

Featured Publications

Designing subject-independent Brain-Computer In- terfaces remains to be an open question for developing systems that can capture the inter-subject intrinsic brain features and classify them with reasonable accuracy. This paper presents the application of the state-of-the-art deep transfer learning archi- tectures on classifying ERP signals. We report 66.87%, 67.64%, 65.58%, and 71.93% test classification accuracy for DenseNet121, DenseNet201, Xception, and VGG-16 models, respectively. The experimental results demonstrate the viability of our approach in subject independent ERP-signals classification and suggest the better performance of models with fewer layers in classifying ERP signals.

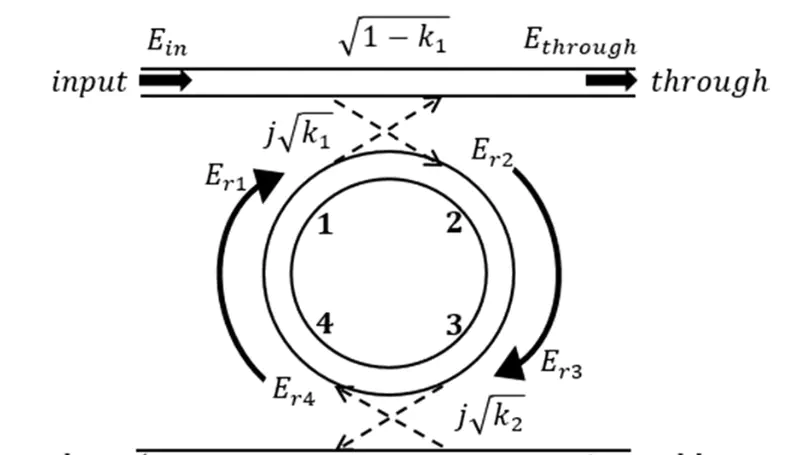

This work proposes electro-optical design of logic gates using micro-ring resonators (MRR). We achieve this through various combinations of MRRs. In order to modulate the rings, thermo-optic effect is utilized. The reported devices are completely CMOS-compat- ible and can be fabricated using existing technologies. We also provide static responses to explain the device working principles. By plotting dynamic response spectra, the per- formance of each device is examined. The proposed logic elements are able to operate at 0.4 Mbps.

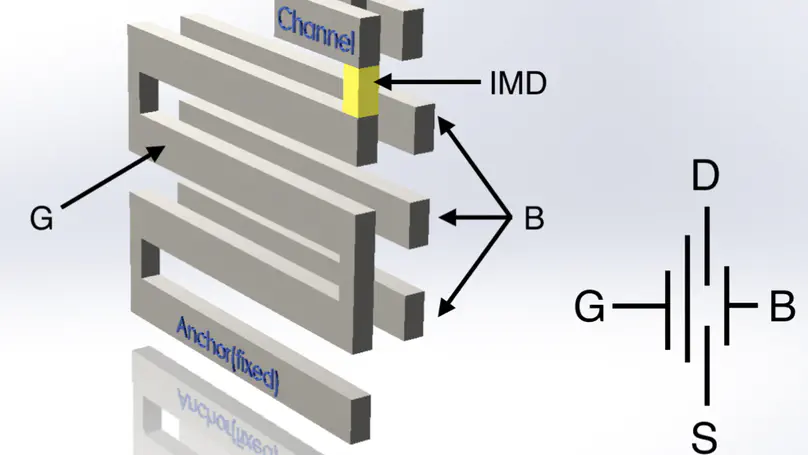

In the past few years, Back-End-of-Line (BEOL) Nano-electromechanical (NEM) relays have emerged as promising switching devices for the beyond-CMOS era, due to their zero- leakage current property, and the compatibility to CMOS fabrication processes. Though the mechanical movement causes the relays to be inherently slower than transistors, the metallic contact interface untethers the limitation on gate-to-drain voltage, which makes the relays capable of handling higher voltages. In this work, we propose novel designs for BEOL NEM relay-based inductorless DC-DC converters for on-chip voltage conversions. The design, implementation, and analysis of buck (step-down) and boost (step-up) converters are shown. Both converters consist of only four NEM relays, respectively. By utilizing the charge pump topology in a switched-capacitor configuration, the relay converters exhibit lower output ripple and higher efficiency compared to their CMOS counterparts. This is particularly valuable for DC-DC voltage conversions in the Internet of Things chips, where the converter switching frequency is moderate, while the demands for efficiency, area saving, and on-chip integration are high.